図研は、東京工業大学 科学技術創成研究院の大場 隆之特任教授を中心に、次世代半導体の研究開発に取り組む産学研究プラットフォーム「WOWアライアンス」に参画し、独自の三次元大規模集積技術の共同開発を進めていることを発表した。

現在、半導体開発は、微細化による高性能化の限界と言われるなかで、チップを縦方向に積層して実装する三次元実装技術への期待が高まっている。

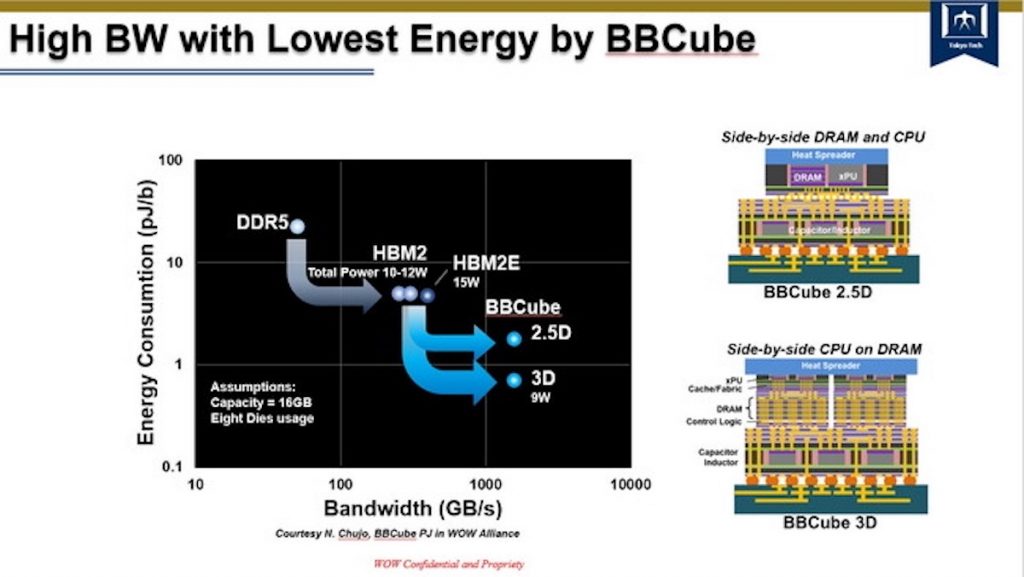

一方、三次元集積による高性能化と同時に求められるのが、消費電力の抑制と熱抵抗の低減であり、WOWアライアンスでは、こうした課題を解決するための、新たなチップレット集積技術の開発に取り組んでいるという。

WOWアライアンスは、ウエハーを従来の20~30μmから4μmまで超薄化する独自の「ウエハー薄化技術」、バンプを用いずTSV配線する「バンプレス配線技術」、高密度超並列配線による「テラバイト高帯域伝送」をWOW(Wafer on Wafer)やCOW(Chip on Wafer)の積層に適用することで、三次元大規模集積技術「BBCube」を確立。

この技術を進化させることで、半導体システムを1000分の1に超小型化し、消費電力は1000分の1以下にすることを目指して、研究開発を進めているという。

図研は、この三次元集積回路の実装設計において、マルチボード設計環境「CR-8000 Design Force」を活用し、技術開発を支援しているとのことだ。

また、3DICやチップレットなどの他、半導体/SiP/PCB/メカの協調設計を支援するCR-8000 Design Forceについては、半導体パッケージング・実装技術の大型イベント「APCS」においてブース出展し、紹介するとしている。

■SEMICON Japan / APCS(Advanced Packaging and Chiplet Summit)

日時:2022年12月14日〜16日 10:00~17:00

場所:東京ビッグサイト 東1・2・3ホール

図研ブース:東2ホール 小間番号1235 / 1246